PCB-Technologietrends entwickeln sich

Dünne Linie

Alle Leiterplatten sind für dünne Linien mit hoher Dichte entwickelt worden, und HDI-Karten sind besonders prominent. Die Definition der HDI-Platine vor einem Jahrzehnt lautete, dass die Linienbreite / der Zeilenabstand 0,1 mm / 0,1 mm und weniger betrug, und jetzt liegt die Industrie im Wesentlichen bei 60 & mgr; m und der Vorschub bei 40 & mgr; m.

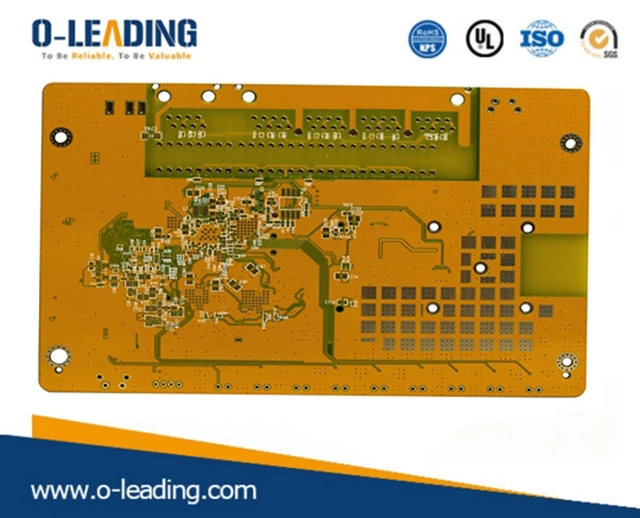

Mehrschicht-Leiterplattenhersteller in China

Die Ausbildung von Leiterplatten-Leiterbildern ist traditionell der chemische Ätzprozess (Subtraktionsverfahren) auf dem Kupferfoliensubstrat. Diese Praxis hat viele Prozesse, ist schwer zu kontrollieren und hat hohe Kosten. Die derzeitige Herstellung von feinen Linien ist tendenziell halbadditiv oder verbessert, wenn sie halb verarbeitet werden.

Die Bindungskraft zwischen dem Leiter und dem isolierenden Substrat ist üblich, indem die Oberflächenrauheit erhöht wird, um die Oberfläche zu vergrößern und die Bindungskraft zu verbessern, wie beispielsweise die Verstärkung der Oberfläche der aufgerauten Harzschicht durch Dekontaminationsbehandlung und die Behandlung der Kupferoberfläche mit einem hohen Profil Kupferfolie oder Oxidation. Bei dünnen Drähten garantiert diese physikalische Methode, dass das Bonden nicht akzeptabel ist. Auf diese Weise wurde eine kupferbeschichtete, stark haftende Kupferfolie auf einer glatten Harzoberfläche entwickelt. Wenn es eine "molekulare Verbindungstechnik" gibt, wird die Oberfläche des Harzsubstrats chemisch behandelt, um eine funktionelle Gruppe zu bilden, die eng an die Kupferschicht gebunden werden kann.

Darüber hinaus ist die Übertragung von Trockenfilmbildern während des Produktionsprozesses für dünne Linien und die Oberflächenbehandlung von Kupferfolie einer der Schlüsselfaktoren für den Erfolg. Die beste Kombination aus Oberflächenreiniger und Mikrozähler wird verwendet, um eine saubere Oberfläche mit ausreichender Fläche zur Verfügung zu stellen, um die Haftung des Trockenfilms zu fördern. Die Oberflächenanlaufschutzbehandlungsschicht der Kupferfolie wird durch chemische Reinigung entfernt und der Schmutz und das Oxid werden entfernt, und ein geeigneter chemischer Reiniger wird entsprechend dem Typ der Kupferfolie ausgewählt, gefolgt von einem Mikroätzen der Oberfläche der Kupferfolie Kupferfolie. Um den belichteten Trockenfilm und die Kupferschicht, das Lötstopplackmuster und die dünne Linie zuverlässig zu machen, sollte auch ein Verfahren zum nicht-physikalischen Aufrauhen der Oberfläche verwendet werden.

Substrat mit semi-additivem Laminat

Gegenwärtig besteht der Hotspot des semi-additiven Verfahrens darin, einen isolierenden dielektrischen Film zum Laminieren zu verwenden, und SAP ist hinsichtlich der Implementierung der Feinlinien und der Herstellungskosten vorteilhafter als MSAP. Das SAP-Laminat verwendet ein duroplastisches Harz, um Kontaktlöcher und Schaltungsmuster durch Laserbohren von Kupfer zu bilden.

Gegenwärtig verwenden internationale HDI-Laminatmaterialien Epoxidharz mit unterschiedlichen Härtungsmitteln, wobei anorganisches Pulver hinzugefügt wird, um die Materialsteifigkeit zu verbessern und den CTE zu reduzieren, und Glasfasergewebe zur Erhöhung der Steifigkeit verwendet werden.

Kupfer überzogenes Loch

Aus Gründen der Zuverlässigkeit werden Verbindungslöcher aus der galvanischen Kupferfilet-Technologie hergestellt, einschließlich Jalousie über Kupfer und Via-Füllkupfer.

Die Fähigkeit, Kupferlöcher zu füllen, liegt in der Füllung: ob Hohlräume in den durch Kupfer geschlossenen Löchern vorhanden sind; Ebenheit: Grübchengrad in der verkupferten Öffnung; Verhältnis von Dicke zu Durchmesser: Dicke (Lochtiefe) und Öffnungsanteil.

IC-Trägerplatinen-Technologie mit invertiertem Chip-Gehäuse

Organische Substrate in globalen Halbleitergehäusen machen mehr als ein Drittel des Marktes aus. Mit der steigenden Produktion von Mobiltelefonen und Tablets stiegen FC-CSP und FC-PBGA signifikant an. Der Packungsträger ersetzt das Keramiksubstrat durch ein organisches Substrat, und der Abstand des Packungsträgers wird immer kleiner, und die typische Linienbreite / Linienteilung beträgt jetzt 15 μm.

Zukünftige Entwicklungstrends. Der BGA- und CSP-Feinpechträger wird fortgesetzt, während die kernlose Platte und vier oder mehr Trägerplatten mehr verwendet werden. Die Roadmap zeigt, dass die Trägerplatine kleinere Strukturgrößen aufweist und der Leistungsfokus eine geringe Dielektrizitätskonstante und einen niedrigen Wert erfordert. Der Wärmeausdehnungskoeffizient und die hohe Hitzebeständigkeit verfolgen ein kostengünstiges Substrat, das auf der Erreichung der Leistungsziele basiert.

Anpassung an Hochfrequenz- und Hochgeschwindigkeitsanforderungen

Die elektronische Kommunikationstechnologie reicht von drahtgebunden bis drahtlos, von niedriger Frequenz, niedriger Geschwindigkeit bis zu hoher Frequenz und hoher Geschwindigkeit. Jetzt ist die Leistung von Mobiltelefonen in 4G eingegangen und wird sich in Richtung 5G bewegen, was eine höhere Übertragungsgeschwindigkeit und größere Übertragungskapazität bedeutet. Mit dem Beginn der globalen Cloud-Computing-Ära hat sich der Datenverkehr verdoppelt, und die Hochgeschwindigkeits- und Hochgeschwindigkeitskommunikationsausrüstung ist ein unvermeidlicher Trend. PCB eignet sich für Hochfrequenz- und Hochgeschwindigkeitsübertragung. Neben der Reduzierung von Signalinterferenzen und -verlusten beim Schaltungsdesign, der Aufrechterhaltung der Signalintegrität und der Leiterplattenherstellung zur Erfüllung der Designanforderungen ist es wichtig, Hochleistungssubstrate zu haben.

Um die Erhöhung der Geschwindigkeit und Signalintegrität der Leiterplatte zu lösen, wird hauptsächlich das elektrische Signalverlustattribut berücksichtigt. Die Schlüsselfaktoren für die Substratauswahl sind die Dielektrizitätskonstante (Dk) und der dielektrische Verlust (Df). Wenn Dk unter 4 liegt und Df unter 0,010 liegt, handelt es sich um ein mittleres Dk / Df-Laminat. Wenn Dk niedriger als 3,7 ist und Df kleiner als 0,005 ist, ist es niedriger Dk /. Df Grade Laminat.

Die Oberflächenrauheit (Profil) des Kupferleiters in Hochgeschwindigkeits-Leiterplatten ist ebenfalls ein wichtiger Faktor, der den Signalübertragungsverlust beeinflusst, insbesondere bei Signalen über 10 GHz. Die Rauheit der Kupferfolie muss bei 10 GHz kleiner als 1 μm sein, und die Verwendung von ultraplanarer Kupferfolie (Oberflächenrauheit 0,04 μm) ist effektiver.