Passaggi dell'integrità del segnale del PCB

o-leader

o-leading.com

2018-07-23 14:22:41

Prima che il progetto inizi, è necessario riflettere e determinare la strategia di progettazione per guidare elementi quali la selezione dei componenti, la selezione dei processi e il controllo dei costi di produzione delle schede.

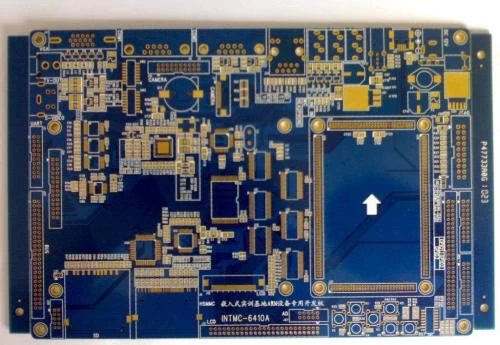

2. la cascata della scheda

Nel caso ideale del segnale completo, tutti i nodi ad alta velocità dovrebbero essere instradati all'interno dello strato interno di controllo dell'impedenza (ad es. Stripline). Per ottimizzare il SI e mantenere la scheda disaccoppiata, il piano di massa / piano di potenza deve essere posizionato il più possibile in coppia. Se hai solo un paio di aerei da piano terra / potenza, sarai lì solo. Se non vi è alcun livello di potenza, è possibile che si riscontrino problemi SI per definizione. Potresti anche incontrare situazioni in cui è difficile simulare o simulare le prestazioni di una scheda prima che venga definito il percorso di ritorno del segnale.

3. controllo della discontinuità e dell'impedenza

L'accoppiamento da linee di segnale adiacenti causerà il crosstalk e cambierà l'impedenza delle linee di segnale. L'analisi di accoppiamento delle linee di segnale parallele adiacenti può determinare la spaziatura "sicura" o prevista (o lunghezza di instradamento parallelo) tra le linee di segnale o tra vari tipi di linee di segnale. Ad esempio, per limitare la diafonia dell'orologio al nodo del segnale dati entro 100 mV, ma per mantenere parallele le tracce del segnale, è possibile calcolare la spaziatura minima consentita tra i segnali su un determinato livello di cablaggio mediante calcolo o simulazione.Produttore di circuiti stampati

)

4. nodi importanti ad alta velocità

Ritardo e inclinazione sono fattori chiave che devono essere considerati per il routing dell'orologio. A causa dei rigidi requisiti di temporizzazione, tali nodi tipicamente devono utilizzare dispositivi di terminazione per ottenere la migliore qualità SI. Questi nodi sono predeterminati e il tempo richiesto per regolare il posizionamento e il routing dei componenti è pianificato per regolare il puntatore per la progettazione dell'integrità del segnale.

Diverse tecnologie di guida sono adatte a diversi compiti. Il segnale è point-to-point o point-to-multiplo? Il segnale è emesso dalla scheda o sulla stessa scheda? Qual è l'intervallo di tempo e il margine di rumore consentiti? Come linea guida generale per la progettazione dell'integrità del segnale, più lenta è la velocità di conversione, migliore è l'integrità del segnale. Un dispositivo di controllo della velocità di variazione 2-3NS è abbastanza veloce da garantire la qualità del SI e aiutare a risolvere problemi quali l'uscita sincrona di commutazione (SSO) e la compatibilità elettromagnetica (EMC).

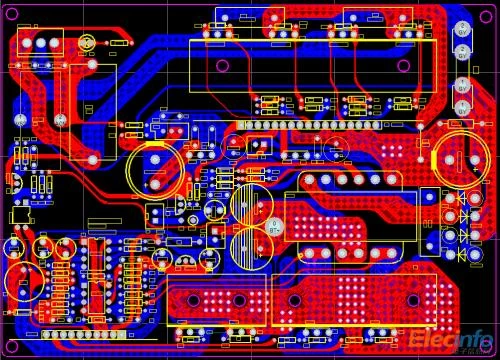

6. fase pre-cablata

Il processo di base della pianificazione SI pre-cablaggio consiste nel definire prima la gamma dei parametri di ingresso (ampiezza, impedenza, velocità di tracciamento) e il possibile raggio topologico (lunghezza min / max, lunghezza della linea corta, ecc.), Quindi eseguire ogni combinazione di simulazione possibile , analizzare i risultati della simulazione di timing e SI, infine trovare un intervallo di valori accettabile.

Successivamente, l'intervallo di lavoro viene interpretato come i vincoli di cablaggio del layout PCB. Questo tipo di preparazione "di pulizia" può essere eseguita utilizzando diversi strumenti software e il programma di routing può gestire automaticamente tali vincoli di cablaggio. Per la maggior parte degli utenti, le informazioni di temporizzazione sono in realtà più importanti dei risultati SI e i risultati della simulazione di interconnessione possono modificare l'instradamento per regolare i tempi del percorso del segnale.

In altre applicazioni, questo processo può essere utilizzato per determinare il posizionamento di pin o dispositivi che non sono compatibili con i puntatori di sincronizzazione del sistema. A questo punto, è possibile determinare completamente i nodi che devono essere instradati manualmente oi nodi che non devono essere terminati. Per i dispositivi programmabili e ASIC, la scelta del driver di uscita può anche essere regolata a questo punto per migliorare la progettazione SI o evitare dispositivi di terminazione discreti.

Simulazione 7.SI dopo il cablaggio

In generale, le linee guida per la progettazione SI sono difficili da garantire che non si verifichino problemi di sincronizzazione o SI dopo il completamento del cablaggio effettivo. Anche se il design è guidato dalla guida, a meno che non sia possibile continuare a controllare automaticamente il design, non è garantito che il design rispetterà pienamente le linee guida, pertanto si verificheranno inevitabilmente problemi. Le verifiche di simulazione SI post-cablaggio consentiranno di prevedere interruzioni (o modifiche) pianificate nelle regole di progettazione, ma ciò è necessario solo per considerazioni di costo o requisiti di cablaggio rigorosi (scheda pcb Società di stampa Cina)

Prendendo le misure di cui sopra può garantire la qualità di progettazione SI della scheda. Una volta completato l'assemblaggio della scheda, è ancora necessario posizionare la scheda sulla piattaforma di test, utilizzando un oscilloscopio o TDR (riflettometro del dominio del tempo) per misurare le reali aspettative della scheda e della simulazione. I risultati sono stati confrontati. Queste misurazioni aiutano a migliorare il modello e i parametri di produzione in modo da poter prendere decisioni migliori (meno vincoli) nel prossimo sondaggio di pre-progettazione.

9.la scelta del modello

Esistono molti articoli sulla selezione dei modelli e gli ingegneri che hanno una verifica della temporizzazione statica potrebbero aver notato che sebbene sia possibile ottenere tutti i dati dalla tabella dei dati del dispositivo, è ancora difficile creare un modello. Il modello di simulazione SI è esattamente l'opposto. Il modello è facile da costruire, ma i dati del modello sono difficili da ottenere. Essenzialmente, l'unica fonte affidabile di dati del modello SI è il fornitore IC, che deve mantenere una tacita comprensione con il progettista. Lo standard del modello IBIS fornisce un supporto dati coerente, ma la creazione del modello IBIS e la garanzia della sua qualità sono costose. I fornitori di circuiti integrati hanno ancora bisogno della domanda del mercato per questo investimento, ei produttori di circuiti stampati potrebbero essere gli unici a richiedere. mercato.

Precedente : Problemi di integrità del segnale del PCB