PCB-signaalin eheysvaiheet

o-johtava

o-leading.com

2018-07-23 14:22:41

Ennen suunnittelun aloittamista sinun on harkittava ja määriteltävä suunnittelustrategia ohjaamaan sellaisia asioita, kuten komponenttien valinta, prosessin valinta ja kartonkikustannusten hallinta.

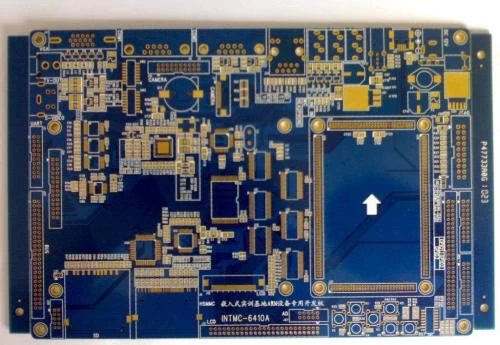

2. laudan kasaus

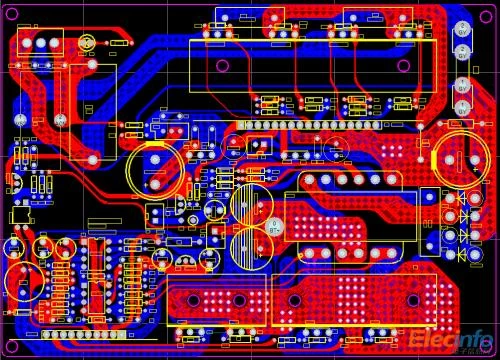

Täydellisen signaalin ihanteellisessa tapauksessa kaikkien suurten nopeuksien solmut tulisi reitittää impedanssisäädin sisäkerrokseen (esim. Liuskajohto). SI: n optimoimiseksi ja levyn irrottamisen vuoksi maataso / voimataso asetetaan pareittain mahdollisimman paljon. Jos sinulla on vain kaksi maatasoa / tehoa, sinä olet vain siellä. Jos tehokerrosta ei ole lainkaan, saatat kohdata SI-ongelmat määritelmän mukaan. Voit myös kohdata tilanteita, joissa on vaikea simuloida tai simuloida aluksen suorituskykyä ennen kuin signaalin paluureitti on määritetty.

3.roststalk- ja impedanssisäätö

Liittäminen viereisistä signaalijohtoista aiheuttaa ylikuulumisen ja muuttaa signaalilinjoiden impedanssia. Viereisten rinnakkaisten signaalilinjoiden kytkentäanalyysi voi määrittää "turvallisen" tai odotetun välimatkan (tai rinnakkaisen reitityspituuden) signaalilinjoiden tai eri tyyppisten signaalilinjoiden välillä. Esimerkiksi keston ylikuulumisen rajoittamiseksi datasignaalisolmulle 100 mV: n rajoissa, mutta signaalin jäljittämisen rinnalla, voit löytää pienimmän sallitun välimatkan minkä tahansa johdotuskerroksen signaalien välillä laskemalla tai simuloimalla (Painettu piirilevyvalmistaja

)

4. tärkeät suurten nopeuksien solmut

Viivästyminen ja vinoutuminen ovat keskeisiä tekijöitä, jotka on otettava huomioon kellon reitityksessä. Tiukat ajoitusvaatimukset huomioon ottaen tällaisten solmujen tyypillisesti on käytettävä päätelaitteita, jotta saavutetaan paras SI-laatu. Nämä solmut ovat ennalta määrätyt, ja kellonaika, joka tarvitaan komponentin sijoittelun ja reitityksen säätämiseen, on tarkoitus säätää osoitinta signaalin eheyden suunnittelua varten.

Erilaiset käyttötekniikat soveltuvat erilaisiin tehtäviin. Onko signaali pisteestä pisteeseen vai pisteestä toiseen? Onko signaali tulostettu laudalta vai samalle levylle? Mikä on sallittu viive ja melumarginaali? Yleisenä ohjeena signaalien eheyden suunnittelulle, sitä nopeampi muunnosnopeus, sitä paremmin signaalin eheys. 2-3NS: n surmattu nopeuden säätölaite on riittävän nopea varmistamaan SI: n laatu ja ratkaisemaan ongelmat kuten synkroninen lähtö (SSO) ja sähkömagneettinen yhteensopivuus (EMC).

6.pre-langallinen vaihe

Ennalta johdotetun SI-suunnittelun perusprosessi on ensin määritellä syöttöparametrialue (aseman amplitudi, impedanssi, seurantanopeus) ja mahdollinen topologinen alue (min / max pituus, lyhyt juovapituus jne.) Ja suorittaa sitten kaikki mahdolliset simulointiyhdistelmät , analysoida ajoitus- ja SI-simulointitulokset, lopulta löytää hyväksyttävän arvojen.

Seuraavaksi työalue tulkitaan PCB-asettelun johdotusrajoituksiksi. Tämäntyyppinen "puhdistus" -valmistus voidaan suorittaa eri ohjelmistotyökaluilla ja reititysohjelma voi käsitellä tällaisia johdotusrajoituksia automaattisesti. Useimmille käyttäjille ajoitustiedot ovat itse asiassa tärkeämpiä kuin SI-tulokset, ja yhteenliittämisen simuloinnin tulokset voivat muuttaa reititystä signaalitien ajoituksen säätämiseksi.

Muissa sovelluksissa tätä prosessia voidaan käyttää määrittämään tapit tai laitteet, jotka eivät ole yhteensopivia järjestelmän ajoituksen osoittimien kanssa. Tässä vaiheessa on mahdollista määritellä kokonaan solmut, jotka täytyy ohjata manuaalisesti tai solmut, joita ei tarvitse lopettaa. Ohjelmoitavissa oleville laitteille ja ASIC-laitteille voidaan myös valita lähtöohjaimen valinta tässä vaiheessa SI-mallin parantamiseksi tai erillisten päätelaitteiden välttämiseksi.

7.SI-simulointi johdotuksen jälkeen

Yleisesti ottaen SI-mallisuuntaviivoja on vaikea varmistaa, ettei SI- tai ajoitusongelmia tapahdu sen jälkeen, kun todellinen kaapelointi on suoritettu. Vaikka suunnitelma ohjaa oppaan, ellet voi jatkaa suunnittelun automaattista tarkistamista, ei ole takeita siitä, että malli noudattaa täysin ohjeita, joten ongelmat tulevat väistämättä esille. Post-johdin SI-simulaatiotarkastukset mahdollistavat suunniteltujen taukojen (tai muutosten) suunnittelusäännöissä, mutta tämä on välttämätön vain kustannusten huomioon ottamiseksi tai tiukkojen johdotusvaatimusten suhteen. (pcb board Painettu yritys kiina)

Edellä mainittujen toimenpiteiden toteuttaminen voi varmistaa levyn SI-suunnittelun laadun. Kun korttikokoonpano on valmis, on edelleen tarpeen sijoittaa levyt testipohjaan oskilloskoopin tai TDR: n (aika-alueen reflektometrin) avulla mitatakseen todellisen kartongin ja simuloinnin odotukset. Tuloksia verrattiin. Nämä mittaukset auttavat sinua parantamaan mallia ja valmistusparametreja, jotta voit tehdä parempia (vähemmän rajoittavia) päätöksiä seuraavassa esisuunnittelustutkimuksessa.

9. mallin valinta

Mallivalikoimasta on monia artikkeleita, ja insinöörit, joilla on staattinen ajastuksen tarkistus, ovat saattaneet huomata, että vaikka on mahdollista saada kaikki tiedot laitteen datataulukosta, on edelleen vaikea rakentaa mallia. SI-simulointimalli on päinvastoin. Mallia on helppo rakentaa, mutta mallidataa on vaikea saada. Pohjimmiltaan ainoa luotettava SI-mallidatan lähde on IC-toimittaja, jonka on säilytettävä hiljainen yhteisymmärrys suunnittelutyöntekijän kanssa. IBIS-mallistandardi tarjoaa yhtenäisen tietovälineen, mutta IBIS-mallin luominen ja sen laadun takaaminen ovat kalliita. IC-toimittajat tarvitsevat edelleen tämän kysynnän markkinoiden kysyntään, ja piirilevyvalmistajat voivat olla ainoita kysynnän haltijoita. markkinoida.