PCBスタックアップ設計

多層PCB回路基板を設計する前に、設計者は、回路サイズ、回路基板サイズ、および電磁両立性(EMC)要件に従って、使用する回路基板の構造を最初に決定する必要があります。つまり、4、6または回路基板の複数の層。層の数を決定したら、内部の電気層の配置と、これらの層に異なる信号を分配する方法を決定します。これは、多層PCBスタック構造の選択です。スタック構造は、PCBボードのEMC性能に影響を与える重要な要素であり、電磁干渉を抑制する重要な手段でもあります。このセクションでは、多層PCBラミネート構造の関連コンテンツを紹介します。電源層とグランド層の数と信号層の数を決定した後、それらの間の相対的な配置は、すべてのPCBエンジニアが避けられないトピックです。

レイヤー配置の一般原則:

1.多層PCBのスタック構造を決定するには、さらに考慮が必要です。配線に関しては、層が多いほど配線は良くなりますが、ボードのコストと難易度も高くなります。製造業者にとって、PCBボードの製造では、スタック構造が対称であるかどうかに注意が向けられているため、最適なバランスを実現するには、層数の選択でさまざまな側面のニーズを考慮する必要があります。経験豊富な設計者は、コンポーネントの事前レイアウトを完了した後、PCBのボトルネックに集中します。他のEDAツールと組み合わせて、回路基板の配線密度を分析します。次に、信号線の数とタイプを、差動線や敏感な信号線などの特別な配線要件と組み合わせて、信号層の数を決定します。次に、電源の種類、絶縁、干渉防止の要件に応じて、内部の電気層の数を決定します。このようにして、回路基板全体の層数が基本的に決まる。

2.コンポーネントの表面(2番目の層)の下はグランドプレーンで、デバイスのシールド層を提供し、最上層の配線の基準面を提供します。敏感な信号層は、内部の電気層(内部電源/接地層)に隣接している必要があります。信号層をシールドする銅膜。回路の高速信号伝送層は、信号の中間層でなければならず、2つの内部電気層の間に挟まれています。このようにして、2つの内部電気層の銅膜は、高速信号伝送のための電磁シールドを提供し、外部への干渉を引き起こすことなく2つの内部電気層間の高速信号放射を効果的に制限できます。

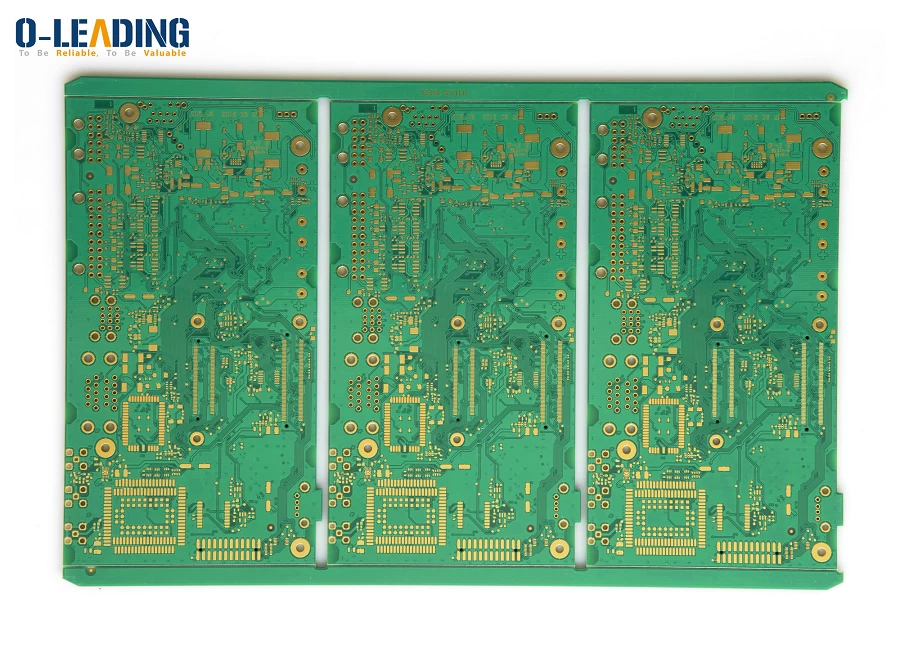

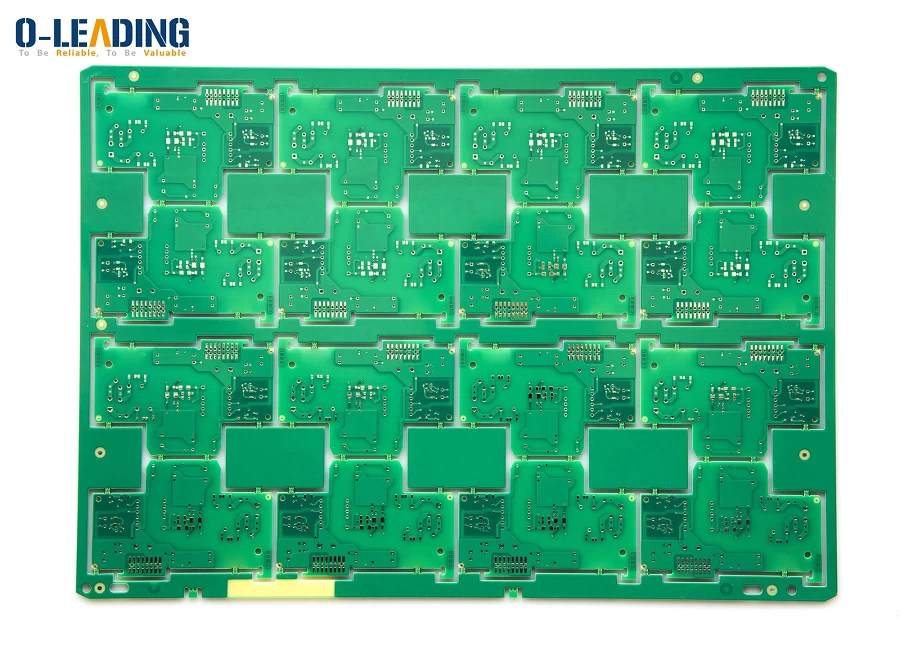

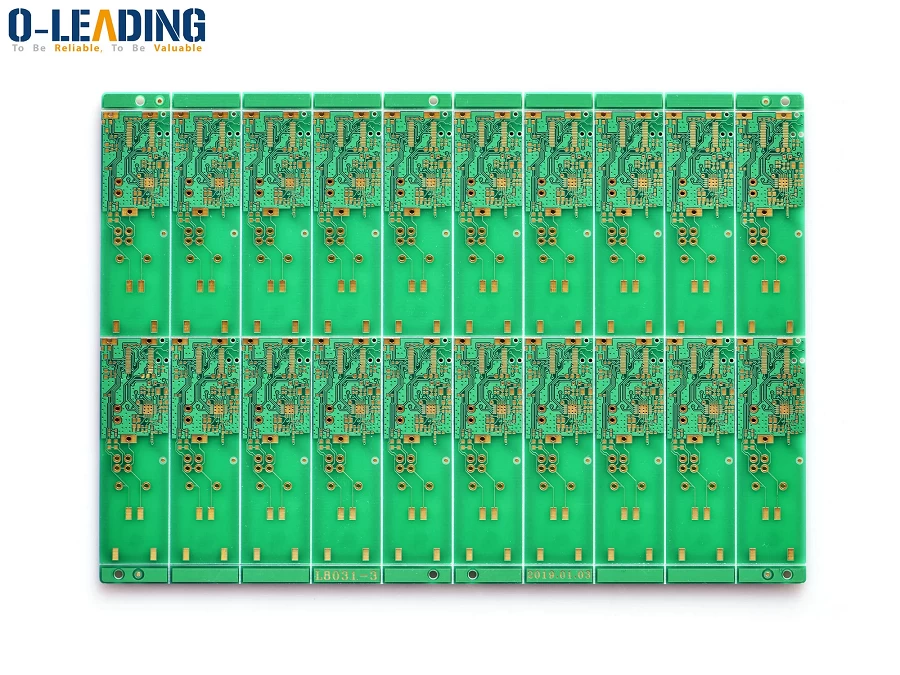

OEM製造Multilayer + PCBボードプリント基板PCB製造

3.すべての信号層は、グランドプレーンにできるだけ近づける必要があります。

4. 2つの信号層が互いに直接隣接しないようにします。クロストークは隣接する信号層間に簡単に導入され、回路機能障害を引き起こします。 2つの信号層の間にグランドプレーンを追加すると、クロストークを効果的に回避できます。 5.主電源は、対応する電源に可能な限り近接します。

6.積層構造の対称性を考慮します。

7.マザーボードの層配置では、既存のマザーボードの並列長距離配線の制御が困難です。ボードレベルの動作周波数が50MHZを超える場合(50MHZ未満の条件については、適切な緩和を参照してください)、推奨されるレイアウトの原則:

*コンポーネント表面と溶接表面は完全な接地面(シールド)です。

*隣接する平行配線層はありません。

*すべての信号層は、グランドプレーンに可能な限り近接しています。

*キー信号は層に隣接しており、パーティションを横断しません。

注:特定のPCB層を設定するときは、上記の原則を柔軟に把握する必要があります。上記の原則を理解した上で、次のような実際のボード要件に応じて:重要な配線層、電源、およびグランドプレーンの分割が必要かどうか層の配置を決定するには、それらを強く動かさないでください。つかまっている。

8.複数の接地された内部電気層は、接地インピーダンスを効果的に低減できます。たとえば、A信号層とB信号層は別々の接地面を使用しているため、コモンモード干渉を効果的に低減できます。