Tipps für das Hochgeschwindigkeits-PCB-Design (> 100 MHz) mit hoher Dichte?

Wenn die Größe der Leiterplatte festgelegt ist und Sie mehr Funktionen im Design berücksichtigen müssen, ist es häufig erforderlich, die Leiterbahndichte der Leiterplatte zu erhöhen. ,

Bei der Entwicklung von Hochgeschwindigkeits- und Hochdichte-Leiterplatten muss Übersprechstörungen besondere Aufmerksamkeit geschenkt werden, da sie sich stark auf das Timing und die Signalintegrität auswirken.

Hier sind ein paar Dinge zu beachten:

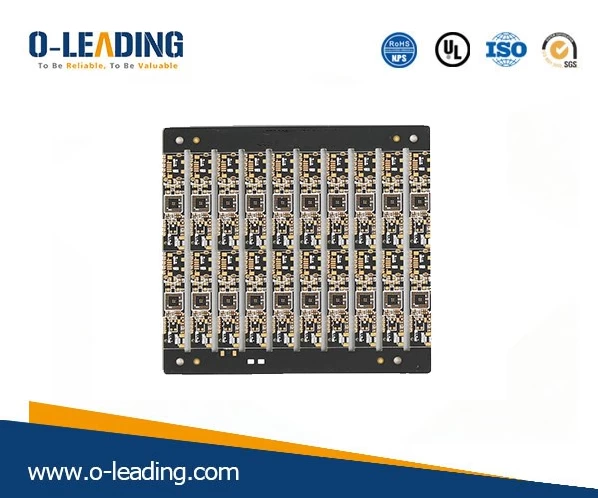

HDI Leiterplattenhersteller China

1. Kontrollieren Sie die Kontinuität und Anpassung der charakteristischen Impedanz der Messkurve.

2. Die Größe des Zeilenabstands. Es ist allgemein bekannt, dass der Abstand doppelt so groß ist wie die Linienbreite. Mithilfe der Simulation können Sie die Auswirkung der Spurteilung auf das Timing und die Signalintegrität verstehen und die minimal tolerierbare Teilung ermitteln. Die Ergebnisse verschiedener Chipsignale können unterschiedlich sein.

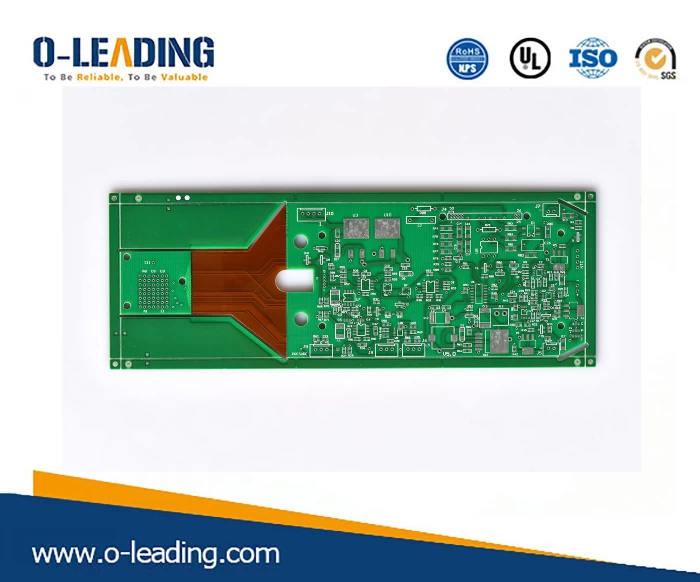

Flexibler Leiterplattenhersteller China

3. Wählen Sie die entsprechende Kündigungsmethode aus.

4. Vermeiden Sie, dass die Richtungen der beiden benachbarten Schichten oben und unten gleich sind, und es gibt sogar Spuren, die sich oben und unten überlappen, da diese Art des Übersprechens größer ist als die der benachbarten Schichten auf derselben Schicht.

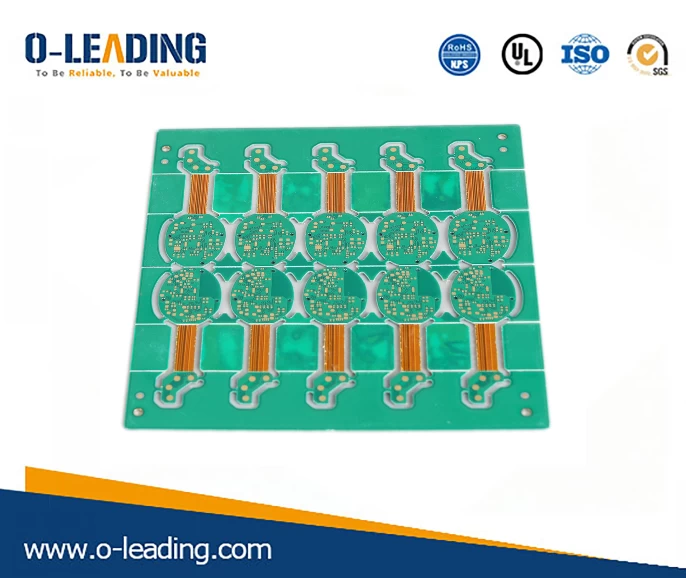

Starr-flexible Leiterplattenfabrik

5. Verwenden Sie Blind / Buried Via, um den Spurenbereich zu vergrößern. Die Herstellungskosten der Leiterplatte werden sich jedoch erhöhen. Es ist wirklich schwierig, vollständige Parallelität und gleiche Länge in der tatsächlichen Implementierung zu erreichen, aber es ist immer noch erforderlich, dies so weit wie möglich zu tun.

Darüber hinaus können ein Differentialabschluss und ein Gleichtaktabschluss reserviert werden, um die Auswirkungen auf das Timing und die Signalintegrität zu verringern