Kuinka parittomat PCB-yhdisteet tasapainottavat pinoamisen ja vähentävät kustannuksia?

Yksi vähemmän dielektristä ja foliokerrosta johtuen parittomien PCB-yhdisteiden raaka-ainekustannukset ovat hieman alhaisemmat kuin parillisten PCB-yhdisteiden. Parittoman kerroksen piirilevyjen käsittelykustannukset ovat kuitenkin huomattavasti korkeammat kuin parillisen kerroksen piirilevyjen. Sisäkerroksen käsittelykustannukset ovat samat; mutta folio / ydinrakenne lisää merkittävästi ulkokerroksen käsittelykustannuksia.

Odd-kerrospiirilevyjen on lisättävä epästandardi laminoitu ydinkerroksen sidosprosessi ytimen rakenneprosessiin. Ydinrakenteeseen verrattuna tehtaan, jossa folio lisätään ydinrakenteen ulkopuolelle, tuotantotehokkuus heikkenee. Ennen laminointia ja liimaamista ulkoinen ydin vaatii lisäkäsittelyä, mikä lisää riskiä, että ulkokerros naarmuuntuu ja syövytyy väärin.

Entä jos suunnittelussa on parittomia PCB-kerroksia? Seuraavia menetelmiä voidaan käyttää tasapainotetun pinoamisen saavuttamiseksi, piirilevyjen valmistuskustannusten vähentämiseksi ja piirilevyjen taivutumisen välttämiseksi.

1) Yksi signaalikerros ja käyttö. Tätä menetelmää voidaan käyttää, jos piirilevyn tehokerros on tasainen ja signaalikerros on pariton. Kerrosten lisääminen ei lisää kustannuksia, mutta se voi lyhentää toimitusaikaa ja parantaa piirilevyjen laatua.

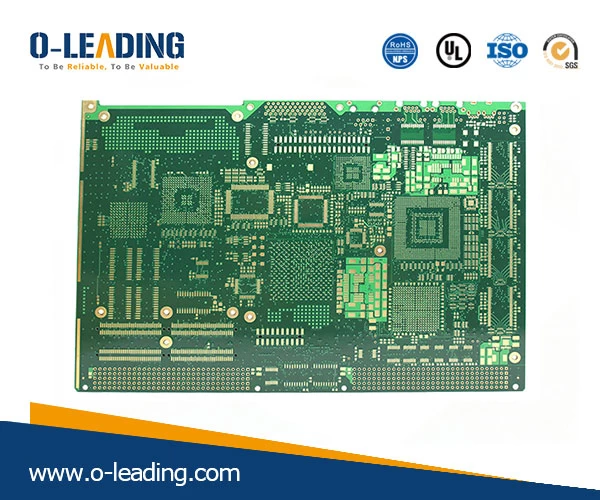

4L monikerroksinen alumiinivalmistaja Kiina

2) Lisää ylimääräinen tehotaso. Tätä menetelmää voidaan käyttää, jos piirilevyn tehokerros on pariton ja signaalikerros on tasainen. Yksinkertainen tapa on lisätä kerros pinnan keskelle muuttamatta muita asetuksia. Reititä ensin piirilevyt parittomien kerrosten mukaan, kopioi sitten pohjakerros keskelle ja merkitse loput kerrokset. Tämä on sama kuin paksunnetun foliokerroksen sähköiset ominaisuudet.

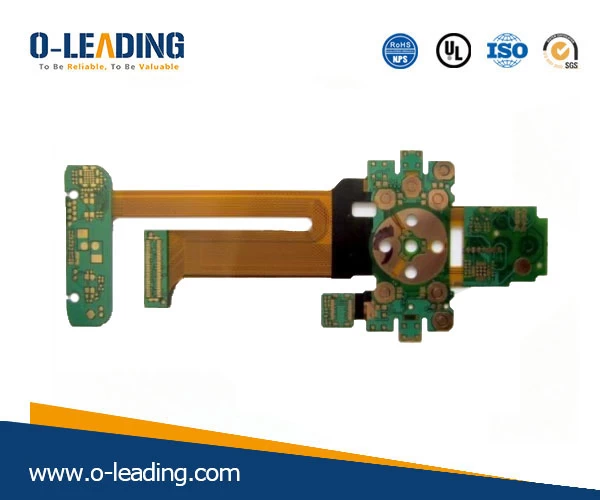

RoHs-yhteensopiva valmistaja Kiina

3) Lisää tyhjä signaalikerros lähellä piirilevyn pinon keskustaa. Tämä menetelmä minimoi pinottamisen epätasapainon ja parantaa piirilevyjen laatua. Reititä kaapelit ensin parittomiin kerroksiin ja lisää sitten tyhjä signaalikerros jäljellä olevien kerrosten merkitsemiseksi. Käytetään mikroaaltopiireissä ja seka dielektrisissä (dielektrisissä dielektrisissä vakioissa) piireissä.