4 suunnittelutekniikat PCB-sähkömagneettisten häiriöiden vähentämiseksi

Siksi sähkömagneettiset häiriöt (EMI) uhkaavat elektronisten laitteiden turvallisuutta, luotettavuutta ja vakautta. Elektroniikkatuotteita suunniteltaessa piirilevyn suunnittelu on ratkaisevan tärkeää EMI-ongelmien ratkaisemiseksi.

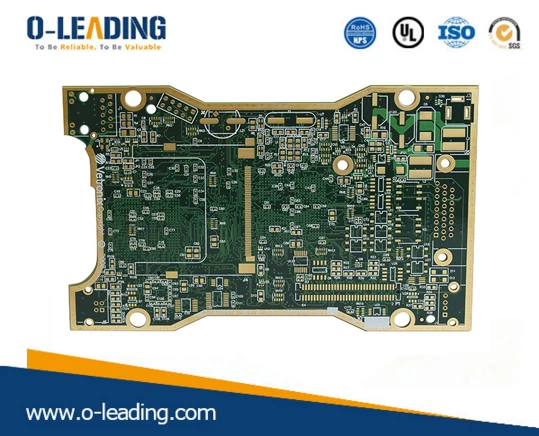

Tämä artikkeli selittää lähinnä PCB: iden suunnittelussa huomioitavia paikkoja, mikä vähentää sähkömagneettisten häiriöiden ongelmaa piirilevyissä. Monikerroksinen PCB-valmistaja Kiinassa.

Sähkömagneettisten häiriöiden määritelmä (EMI)

Sähkömagneettiset häiriöt (EMI, Electro Magne TIc Interference) voidaan jakaa säteilyyn ja johtaa häiriöitä. Säteilevä häiriö on häiriölähde, joka käyttää tilaa väliaineena häiritä sen signaalia toisella sähköverkolla. Johtava interferenssi on johtavan väliaineen käyttö väliaineena häiritsemään yhden sähköverkon signaaleja toiseen. Suurnopeusjärjestelmien suunnittelussa integroidut piiritapit, suurtaajuiset signaalilinjat ja erilaiset pistokkeet ovat yleisiä lähteitä säteilytettyjen häiriöiden muodostumiselle piirilevyjen suunnittelussa. Ne lähettävät sähkömagneettiset aallot ovat sähkömagneettisia häiriöitä (EMI), jotka vaikuttavat itseensä ja muihin järjestelmiin. normaali työ. 3D-tulostimen PCB-toimittaja.

PCB-levyn suunnittelu tekniikat sähkömagneettisille häiriöille (EMI)

EMI-ongelmaan on monia ratkaisuja nykypäivän piirilevyjen suunnittelutekniikoissa, kuten EMI-vaimentavat pinnoitteet, sopivat EMI-vaimennusosat ja EMI-simulointimalli. Selitä lyhyesti nämä vinkit.

1. Yhteisen tilan EMI-häiriölähde (kuten jännitepudotus, joka muodostuu virtakiskoon muodostetusta siirtymäjännitteestä irrotusreitin induktorin läpi)

Alhaisilla induktoreilla tehon tasossa induktorien syntetisoimat transientit vähenevät ja yhteismoodin EMI vähenee.

Pienennä tehokerroksen pituutta IC-virtapistoliitäntöihin.

Käytä 3-6 miljoo- naa PCB-kerroksen väliä ja FR4-dielektristä materiaalia.

Kiina pcb valmistajat.

2, sähkömagneettinen suojaus

Yritä sijoittaa signaalin jäljet samalle PCB-kerrokselle ja lähellä virtaa tai maatasoa.

Tehotason tulisi olla mahdollisimman lähellä maatasoa

3, osien asettelu (erilaiset asettelut vaikuttavat piirin häiriöihin ja häiriöiden estoon)

Lohkokäsittely piirin eri toimintojen mukaisesti (kuten demodulaatiopiiri, korkean taajuuden vahvistinpiiri ja sekoituspiiri jne.), Jossa vahvat ja heikot sähköiset signaalit erotetaan ja digitaaliset ja analogiset signaalipiirit erotetaan.

Jokaisen piirin osan suodatinverkko on kytkettävä lähelle, mikä ei vain vähennä säteilyä, vaan myös parantaa piirin häiriövaikutusta ja vähentää häiriöiden mahdollisuutta.

Häiriöille alttiiden komponenttien tulisi välttää häiriölähteitä, kuten CPU: n häiriöitä tietojenkäsittelylaitteessa asettelun aikana.

4, johdotusnäkökohdat (kohtuuttomat johdotukset aiheuttavat ristiriitoja signaalilinjojen välillä)

Älä jätä jälkiä PCB-levyn reunan läheisyyteen, jotta vältät katkeamisen tuotannon aikana.

Voimajohto on leveämpi ja silmukan vastus vähenee.

Signaalilinjat ovat niin lyhyitä kuin mahdollista ja vias-lukumäärä vähenee.

Kulmajohtojen ei pitäisi olla suorassa kulmassa, ja niiden tulisi olla 135 ° kulmassa.

Digitaalipiiri ja analoginen piiri tulisi eristää maalla, digitaalinen maa ja analoginen maa on erotettava toisistaan ja liitettävä lopulta virtalähteeseen.

Sähkömagneettisten häiriöiden vähentäminen on tärkeä osa piirilevyjen suunnittelua. Niin kauan kuin siirryt suunnittelun puolelle, olet luonnollisesti pätevämpi tuotekokeissa, kuten EMC-testauksessa.