고속 신호용 PCB 설계 문제의 전자기 호환성

오 리드

o-leading.com

2018-06-01 15:21:06

1,3W 및 20H 규칙

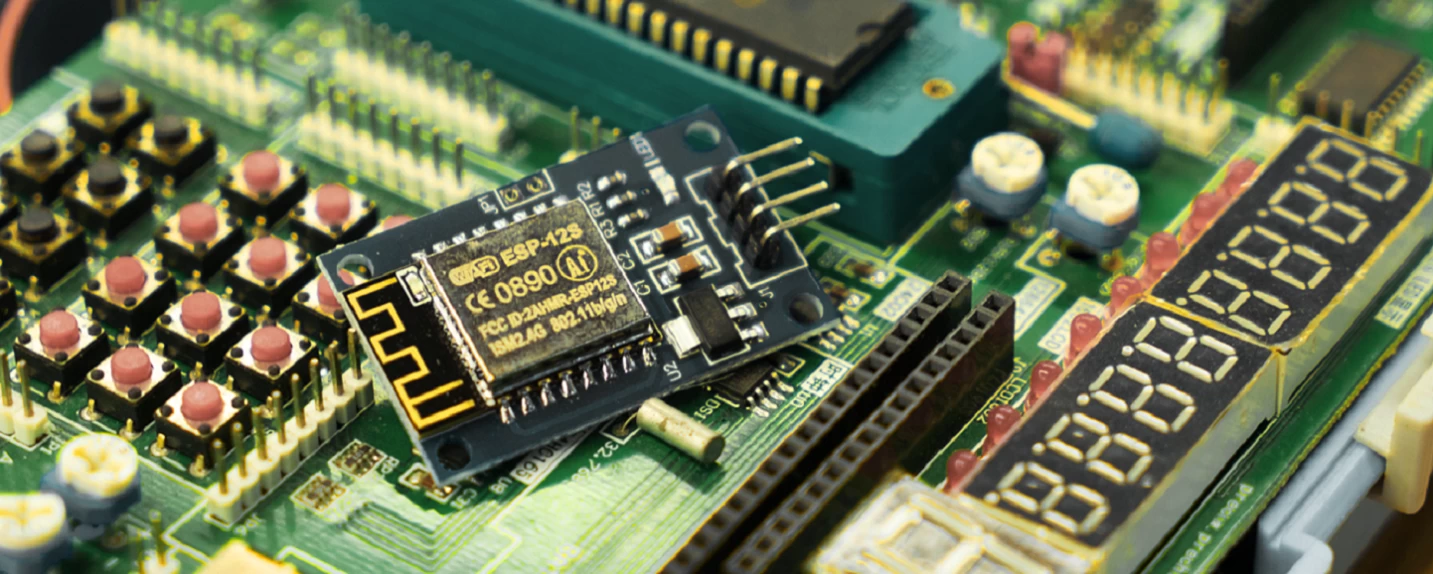

3w는 신호선 사이의 배선 간격이며, 그림 1과 같이 선폭의 두 배, 중심 거리는 3 배입니다.

전자기 호환성 문제는 PCB (고품질의 pcb 제조 업체) 디자인에주의를 기울여야한다.

3W 선 간격은 전계가 다른 간섭 신호에서 70 %를 넘지 않도록합니다. 98 % 전계가 서로 간섭하지 않으면 10W 간격이 사용됩니다.

20H는 다층 기판의 파워면이 두면 사이의 거리보다 20 배 이상 큰 것을 의미합니다. 이러한 방식으로, 전원은 접지면으로 둘러싸여 외부 방사 가능성을 크게 줄입니다. 아래 그림과 같이

PCB 디자인이주의해야하는 전자기 호환성 문제

2, 고속 신호 라우팅 레벨 선택

고속 신호선은 내부 층을 걸을 때 가장 적합하므로 유전체 층이 차폐 역할을하며 EMI 신호의 외부 방출을 효과적으로 억제 할 수 있습니다.

시계 돈과 같은 고속 신호 라인의 경우 패킷 처리를 사용하는 것이 가장 좋으며 패키지는 3000mil마다 접지에 연결됩니다. 3W 규칙은 키 신호와 다른 라인 사이에서 만족되어야합니다. 아래 그림과 같이

PCB 디자인이주의해야하는 전자기 호환성 문제

4, 땅에 금속 껍질.